Open EDA iVerilog

Posted on Sun 21 June 2020 in eda

Tools (MacOSX):

Installation

iVerilog You can nstall it through brew

brew install icarus-verilog

Or MacPorts:

sudo port -v install iverilog

Running a simulation

First compile Verilog using iverilog:

iverilog -o test.vvp test_tb.v

Then running the simulation:

vvp test.vvp

Which should result in the following:

VCD info: dumpfile test.vcd opened for output.

done testing case 0

done testing case 1

done testing case 2

done testing case 3

done testing case 4

done testing case 5

done testing case 6

done testing case 7

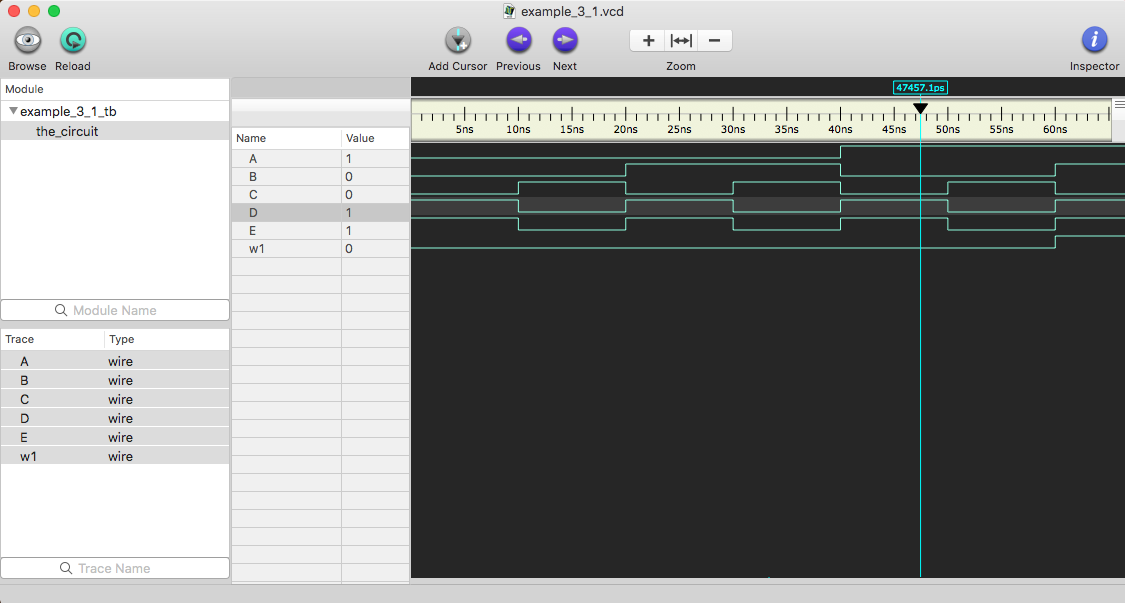

Finally, have a look at waveform:

open -a Scansion test.vcd

More test.v:

module test(A, B, C, D, E);

output D, E;

input A, B, C;

wire w1;

and GATE1(w1, A, B);

not GATE2(E, C);

or GATE3(D, w1, E);

endmodule

And the testbench:

// Verilog test bench for test

`timescale 1ns/100ps

`include "test.v"

module test_tb;

wire A, B, C, D, E;

integer k=0;

assign {A,B,C} = k;

test the_circuit(A, B, C, D, E);

initial begin

$dumpfile("test.vcd");

$dumpvars(0, test_tb);

for (k=0; k<8; k=k+1)

#10 $display("done testing case %d", k);

$finish;

end

endmodule